- Development of Curing Process for EMC Encapsulation of Ultra-thin Semiconductor Package

Seong Yeon Park*, Seung Yoon On*, Seong Su Kim*†

* Department of Mechanical Engineering, KAIST

- 초박형 반도체 패키지의 EMC encapsulation을 위한 경화 공정 개발

박성연*· 온승윤*· 김성수*†

This article is an open access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (http://creativecommons.org/licenses/by-nc/4.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

In this paper, the Curing process for Epoxy Molding Compound (EMC) Package was developed by comparing the performance of the EMC/Cu Bi-layer package manufactured by the conventional Hot Press process system and Carbon Nanotubes (CNT) Heater process system of the surface heating system. The viscosity of EMC was measured by using a rheometer for the curing cycle of the CNT Heater. In the EMC/Cu Bi-layer Package manufactured through the two process methods by mentioned above, the voids inside the EMC was analyzed using an optical microscope. In addition, the interfacial void and warpage of the EMC/Cu Bi-layer Package were analyzed through C-Scanning Acoustic Microscope and 3D-Digital Image Correlation. According to these experimental results, it was confirmed that there was neither void in the EMC interior nor difference in the warpage at room temperature, the zero-warpage temperature and the change in warpage

본 연구에서는 면상 발열체인 CNT Heater를 이용한 EMC 패키지 경화 공정 시스템을 개발하기 위하여, 기존 Hot Press 공정과 CNT Heater 공정 시스템을 통해 제작한 EMC/Cu Bi-layer 패키지의 성능을 비교하여 CNT Heater 공정 시스템의 가능성을 확인하였다. CNT Heater 공정의 경화 사이클을 도출하기 위해 Rheometer를 이용해 EMC의 점성을 측정하였다. 앞서 언급한 두 공정에 의해 성형된 EMC/Cu Bi-layer 패키지에서 EMC 내부의 Void를 광학 현미경으로 분석하였다. 또한, C-Scanning Acoustic Microscope와 3D-Digital Image Correlation를 통해 EMC/Cu Bi-layer 패키지의 계면 Void와 휨을 분석하였다. 이러한 분석 결과를 기반으로, EMC 내부 및 EMC/Cu Bi-layer의 계면에서 Void가 없음을 확인하였으며, 상온에서의 휨 크기, Zero 휨 온도와 휨 크기 변화에서 차이가 없음을 확인하였다

Keywords: EMC/Cu Bi-layer Package, CNT Heater, Hot Press, Void, 휨(Warpage)

최근 개발되고 있는 전자 기기들의 경우, 두께를 줄이기 위해 패키지의 두께를 1 mm 미만으로 제작하고 있다. 반도체를 구성하고 있는 부품들의 소형화에 대한 연구가 지속적으로 진행되어왔지만, 반도체 칩 및 기판의 단위 축소 기술이 한계에 다다르면서 전자 패키징 기술에 대한 관심이 증가하고 있다. 전자 패키징은 반도체를 구성하고 있는 Si Chip, 와이어, 리드프레임 등을 외부 환경으로부터의 전기적 절연을 이루고, 디바이스의 작동 시 발생하는 열을 방출할 수 있으며, 외부 충격으로부터 Chip을 보호하기 위한 공정 단계이다[1,2].

에폭시 기반의 Epoxy Molding Compound (EMC)로 구성된 전자 패키징 공정은 열과 압력을 동시에 가해주어야 하기 때문에 Autoclave, Oven, Hot Press와 같은 경화 공정 장비를 통해 수행되고 있다. 대류로 열전달을 해주는 Autoclave와 Oven을 이용할 경우, 복합재료 성형 과정에서 경화 사이클의 온도 Profile과 복합재료 내의 온도 Profile에서의 차이가 지속적으로 언급되고 있는 문제이며, 또한, 앞서 언급한 경화 공정 장비들은 공정 가능 면적이 장비의 크기에 따라 제한적이며, 전력 소비가 심하다는 단점이 있다[3-5].

이러한 온도 Profile 차이와 과도한 전력 소비 문제를 해결하기 위하여 전기 에너지를 이용해 열을 올려주는 면상 발열체에 대한 관심이 높아지고 있다. 이는 Joule Heating과 Tunneling Effect에 의해 전기 에너지를 열 에너지로 전환하여 온도를 올려주는 것으로 기존의 발열 방법보다 에너지 효율이 우수하며, 적은 에너지로도 원하는 온도를 올릴 수 있으며, 또한, 면상 발열체는 크기에 제한이 없기 때문에 앞서 언급한 장비 크기에 따라 제한되는 공정 가능 면적을 해결할 수 있다는 장점이 있다[6-8].

본 연구에서는 면상 발열체인 CNT Heater를 이용해 EMC 패키지 경화 공정에 적용하고자 한다. 기존 방법인 Hot Press와 새로운 경화 공정 방법인 CNT Heater를 이용해 EMC/Cu Bi-layer 패키지를 제작하였으며, EMC Sheet 내 Void, EMC/Cu Bi-layer Package 계면 Void 그리고 Bi-layer 구조에서 나타나는 휨을 비교하여 EMC 패키지를 위한 새로운 경화 공정 방법에 대한 가능성을 분석하였다.

2.1 EMC/Cu Bi-layer 패키지 제작

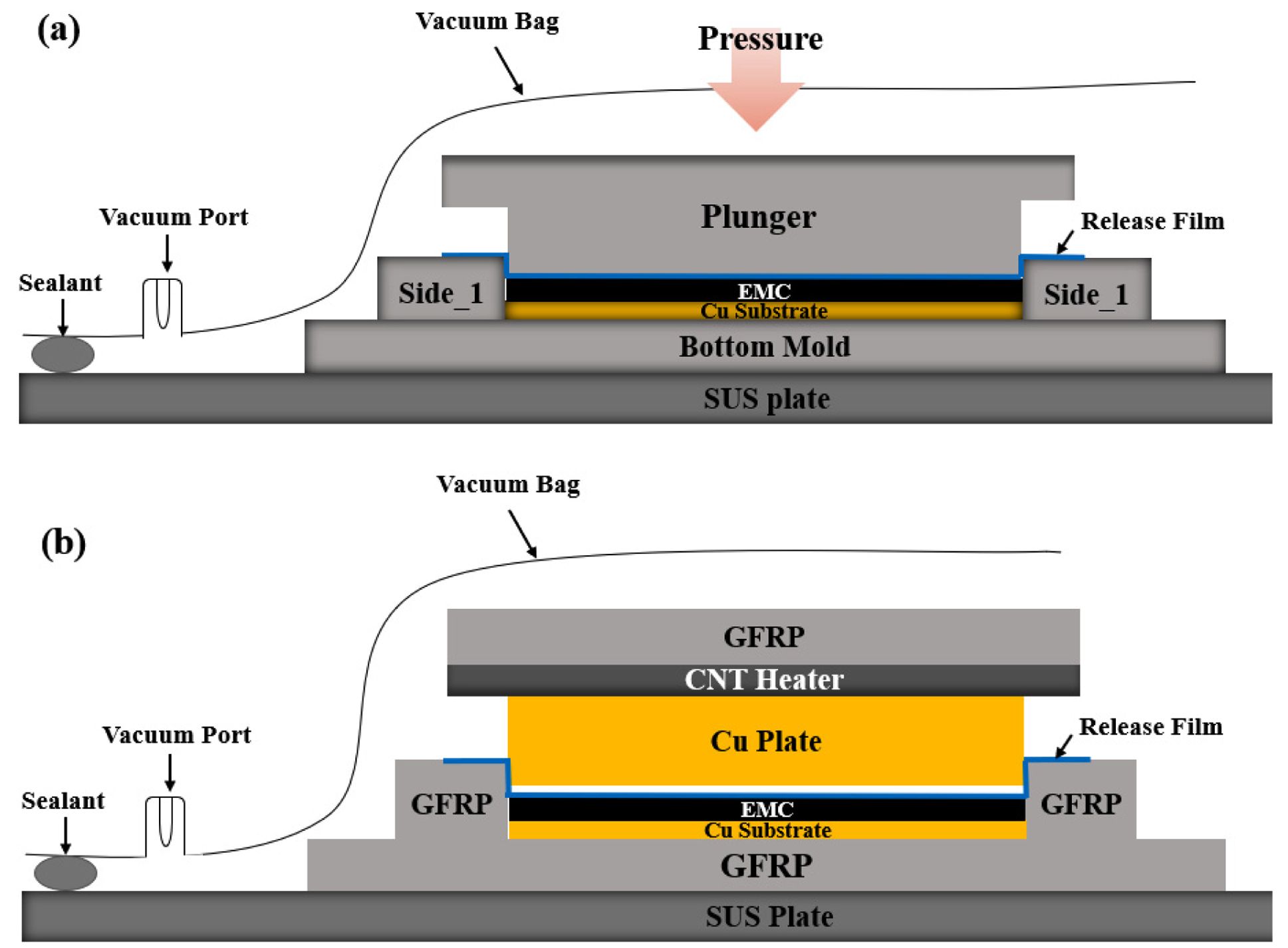

Fig. 1은 Hot Press 공정과 CNT Heater 공정을 도식화한 것이다. EMC 패키지 내 Void를 제거하기 위하여, 두 공정 모두 진공을 잡아주었다. 그리고 Hot Press는 열과 압력을 동시에 가해주었으며, CNT Heater를 발열하기 위해 Power Supply를 이용하였으며, Hot Press처럼 압력을 가해주지 않기 때문에 CNT Heater를 이용한 경화 공정은 진공 압력만으로 진행하였다.

2.2 EMC/Cu Bi-layer 패키지 분석

압력을 가하지 않은 CNT Heater를 이용한 EMC 패키지 경화 공정에 대한 경화 사이클을 도출하기 위하여 Rheometer를 통해 EMC 최저 점도 온도를 측정하였다. 또한, 광학 현미경을 토대로 EMC Sheet 내의 Void를 측정하였다. C-Scanning Acoustic Microscope (C-SAM)를 통해 EMC/Cu Bi-layer 패키지의 계면 Void 여부를 확인하였으며, 3D-Digital Image Correlation (3D-DIC)를 통해 두 공정을 통해 제작한 EMC/Cu Bi-layer의 휨 현상을 분석하였다.

|

Fig. 1 Schematic diagrams of EMC/Cu Bi-layer Package Process; (a) Hot Press, (b) CNT Heater |

3.1 Rheometer 측정을 통한 경화 사이클 도출

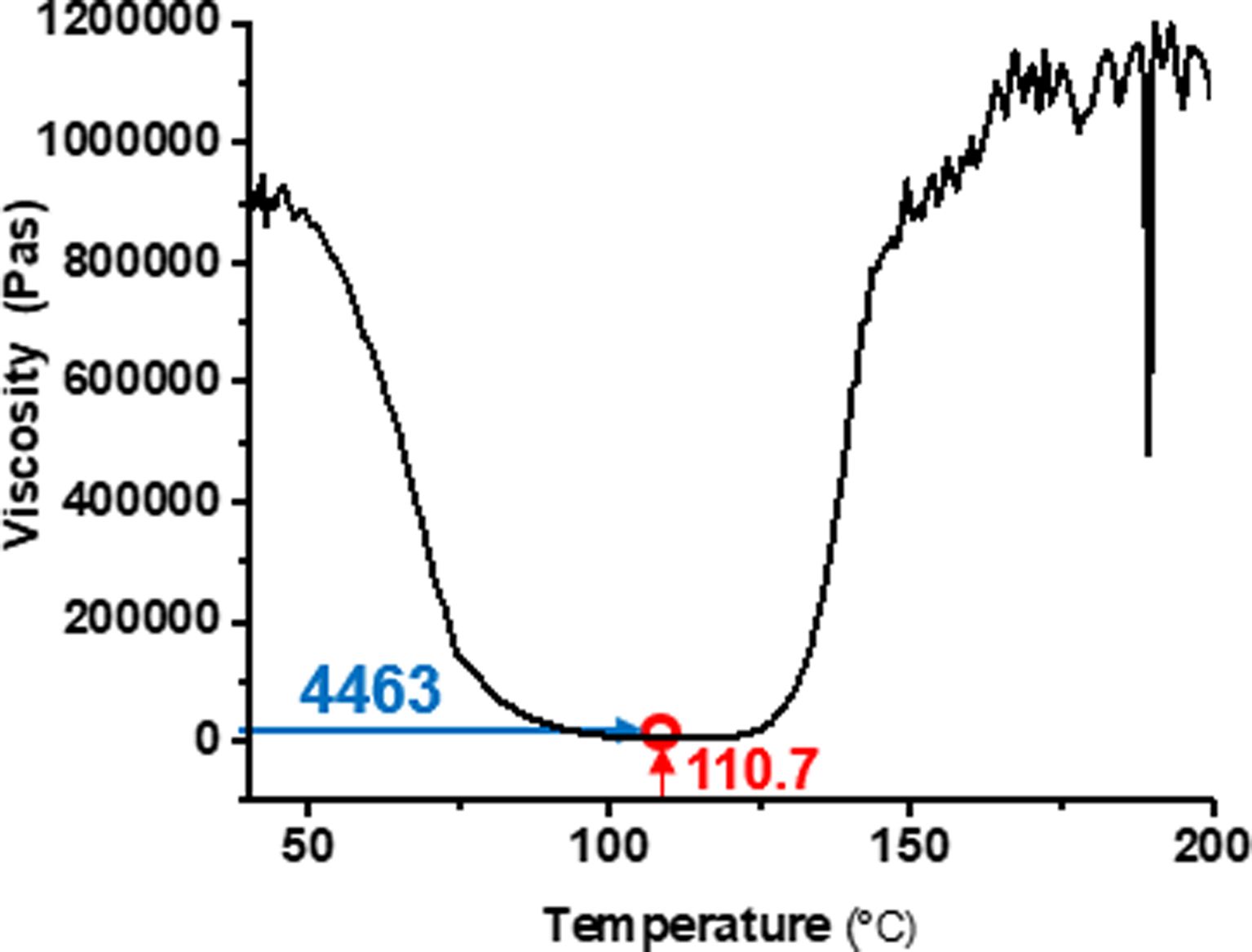

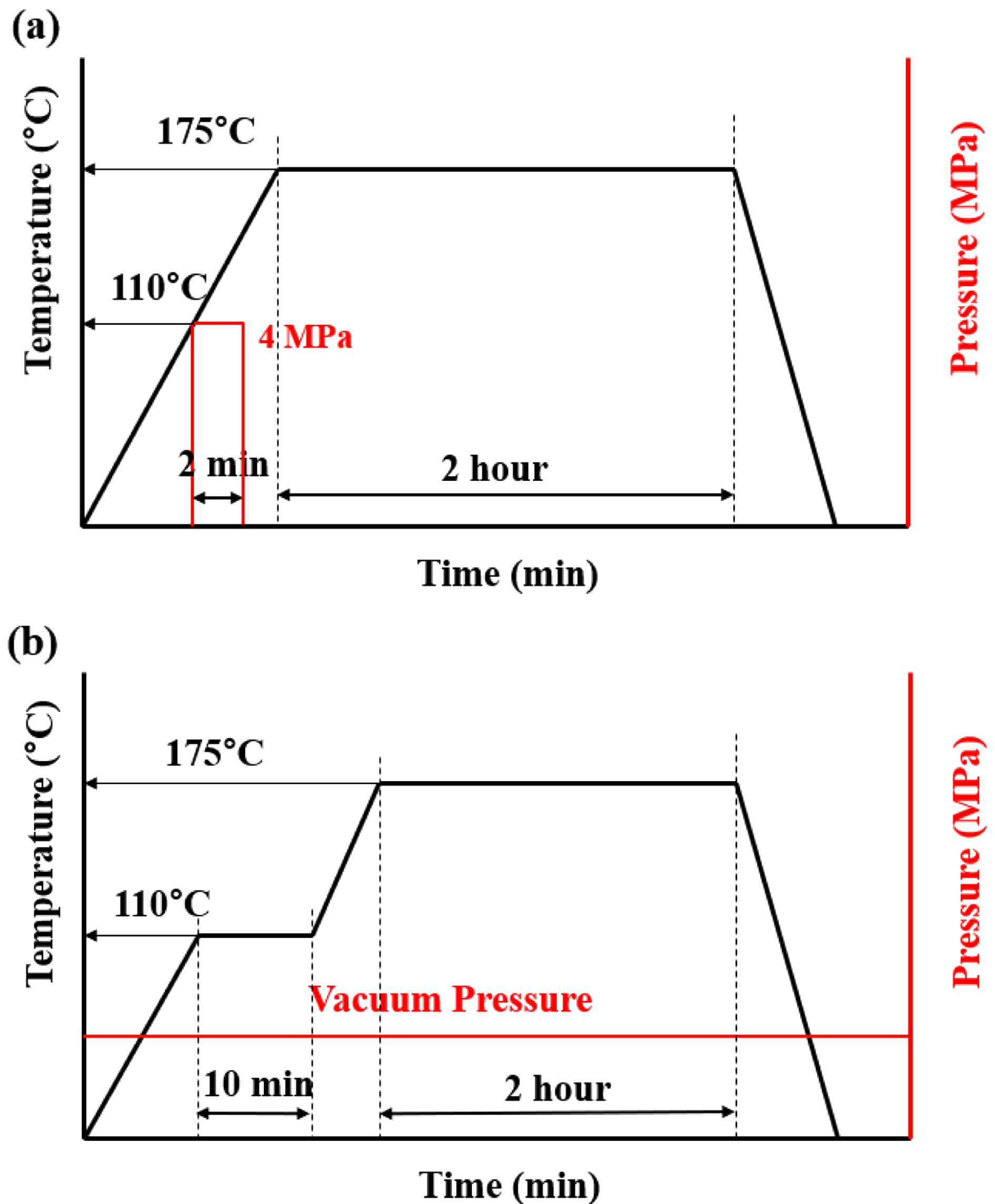

Fig. 2는 Rheometer를 통해 EMC의 점도를 분석한 결과를 나타낸다. 110도에서 최저 점성을 가지는 것을 확인할 수 있었다. 그래서 Fig. 3에서 경화 사이클을 비교하여 나타낸다. 기존 Hot Press 공정은 상온에서 175도까지 승온시켰고, 110도에 도달했을 때 2분동안 4 MPa의 압력을 가해주었다. 이후 175도가 도달한 후, Post Cure 과정으로 2시간동안 유지시켜 주었다. CNT Heater 공정에서는 진공 압력만 가해주기 때문에 앞의 Hot press 공정의 경화 사이클과는 다르게 상온에서 110도까지 승온시켰고, EMC의 최저 점성을 가지는 110도에서 10분간 유지해줌으로써 EMC Package 성형이 이루어지도록 해주었다. 그리고 175도까지 승온시킨 후 Post Cure 과정은 2시간동안 유지시켜 주었다.

3.2 공정 간 EMC 분석

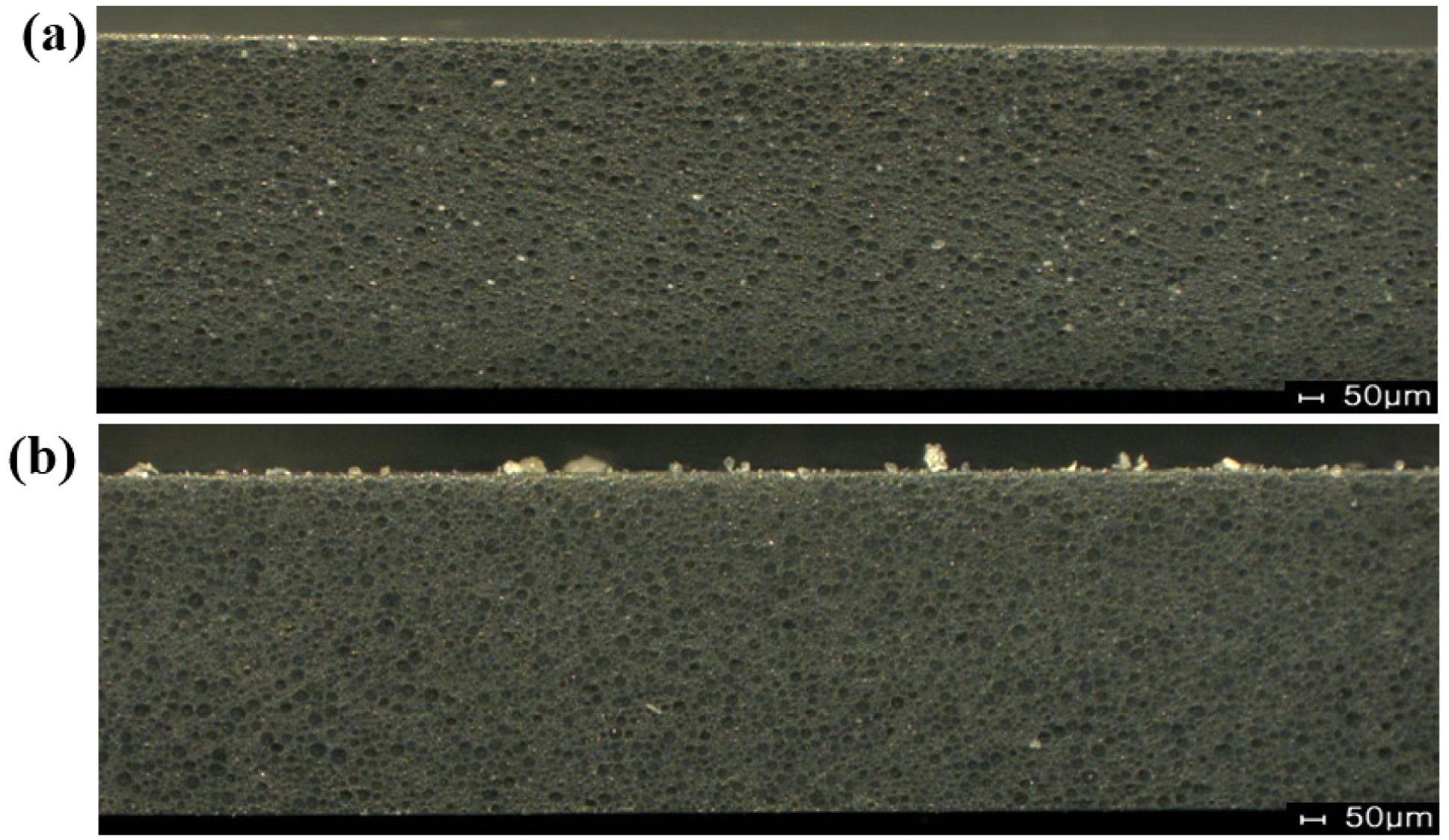

Fig. 4는 광학 현미경을 통해 Hot Press 공정과 CNT Heater 공정으로 제작한 EMC 내의 Void를 나타낸다. 두 공정의 EMC 내부에서의 Void가 없는 것을 확인할 수 있었다

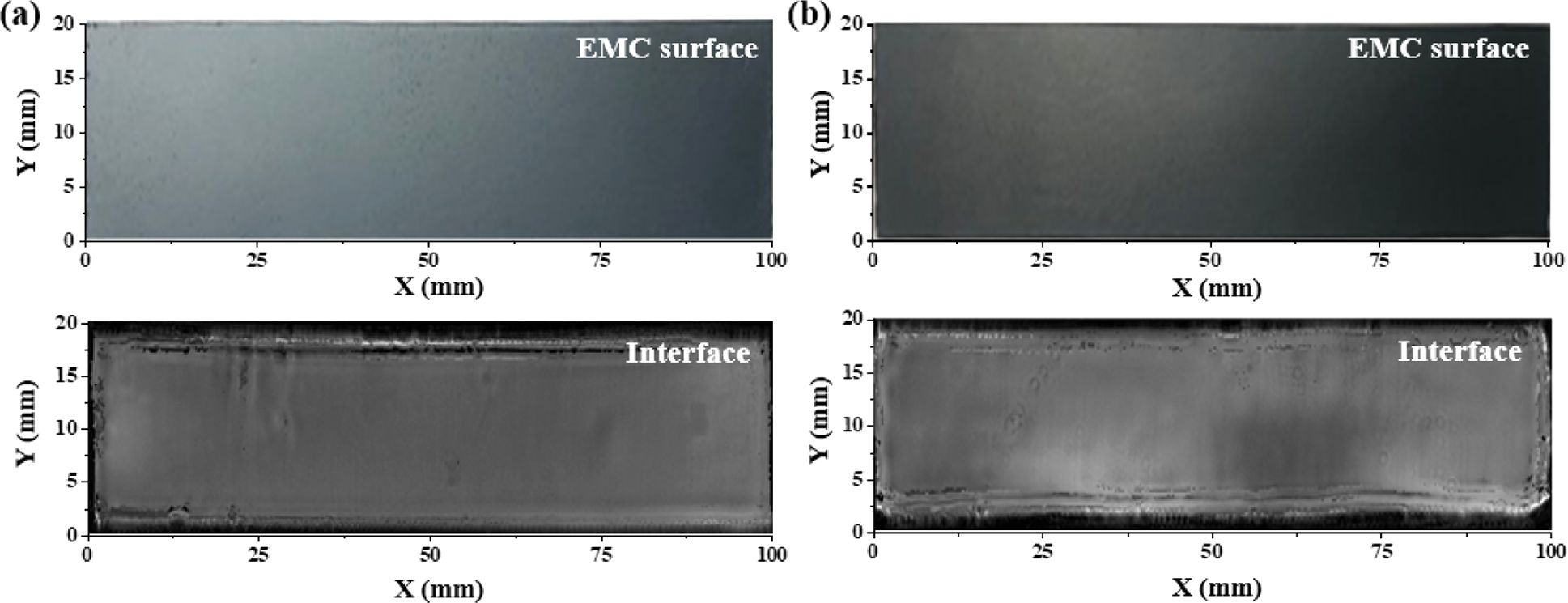

Fig. 5는 두 공정을 통해 제작한 EMC/Cu Bi-layer 패키지의 표면과 계면을 나타낸다. 두 공정 간의 EMC 표면에서는 큰 차이를 보이지 않는 것을 확인할 수 있었다. 또한, 두 공정으로 제작한 EMC/Cu Bi-layer 패키지의 계면에서 Void가 관찰되지 않았음으로 접합이 잘 이루어진 것을 확인할 수 있다.

3.3 휨 분석

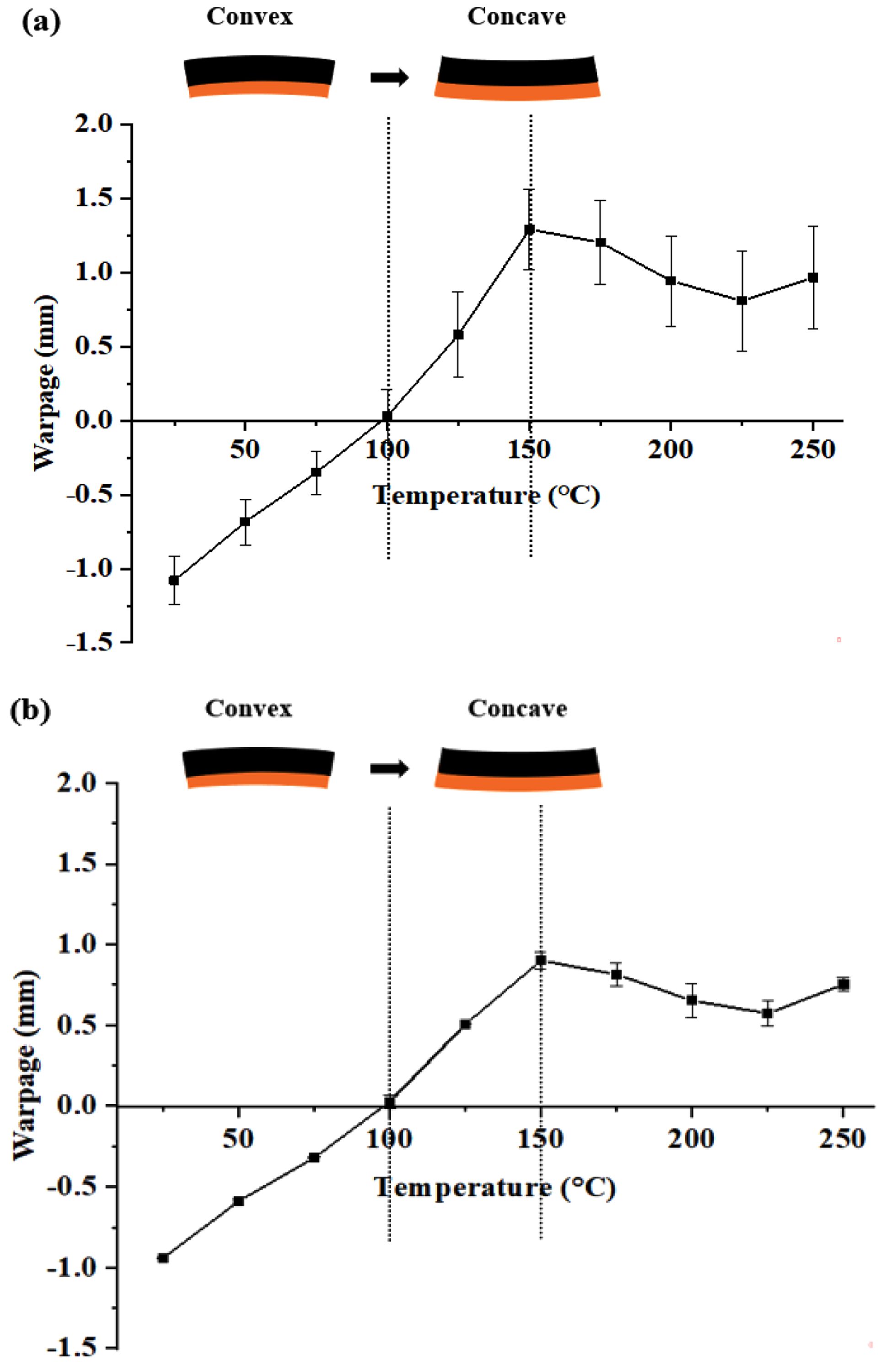

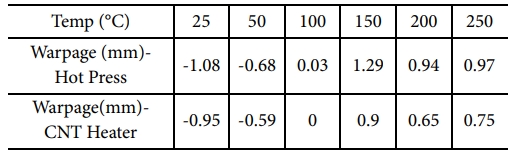

Fig. 6은 공정에 따라 EMC/Cu Bi-layer 패키지의 휨을 3D-DIC로 측정하여 나타낸 것이다. Fig. 6(a)는 Hot Press 공정을 통해 제작한 EMC/Cu Bi-layer 패키지의 휨을 나타낸다. 이종 재료 간의 CTE 차이에 의해서 상온에서는 휨 형태가 Convex 방향이며, Convex에서 Concave로 휨 방향이 바뀌는 Zero 휨 온도는 100도, 패키지의 휨이 증가에서 감소로 바뀌는 온도는 150도로 나타나는 것을 확인할 수 있다. Fig. 6(b)는 CNT Heater 공정을 통해 제작한 EMC/Cu Bi-layer 패키지의 휨을 나타낸다. 앞의 Hot Press공정과 동일하게 상온에서의 휨 형태는 Convex 방향, Convex에서 Concave로 휨 방향이 바뀌는 Zero 휨 온도는 100도, 패키지의 휨이 증가에서 감소로 바뀌는 온도 또한 150도로 동일한 것을 통해 CNT Heater를 통해서도 EMC/Cu Bi-layer 패키지 성형이 가능하다는 것을 확인하였다.

Table 1은 두 공정에 따라 EMC/Cu Bi-layer Package의 휨을 크기를 비교한다. Zero 휨 온도이전에서의 휨 크기는 두 공정 모두 비슷한 경향성을 나타내는 것을 확인할 수 있었다. 그러나 Zero 휨 온도 이후에서의 휨 크기 차이가 점차 커지는 것을 확인할 수 있다. 이는 두 공정 간의 경화 사이클 차이에 의해 발생하는 잔류 응력 차에 의한 것으로 판단이 된다.

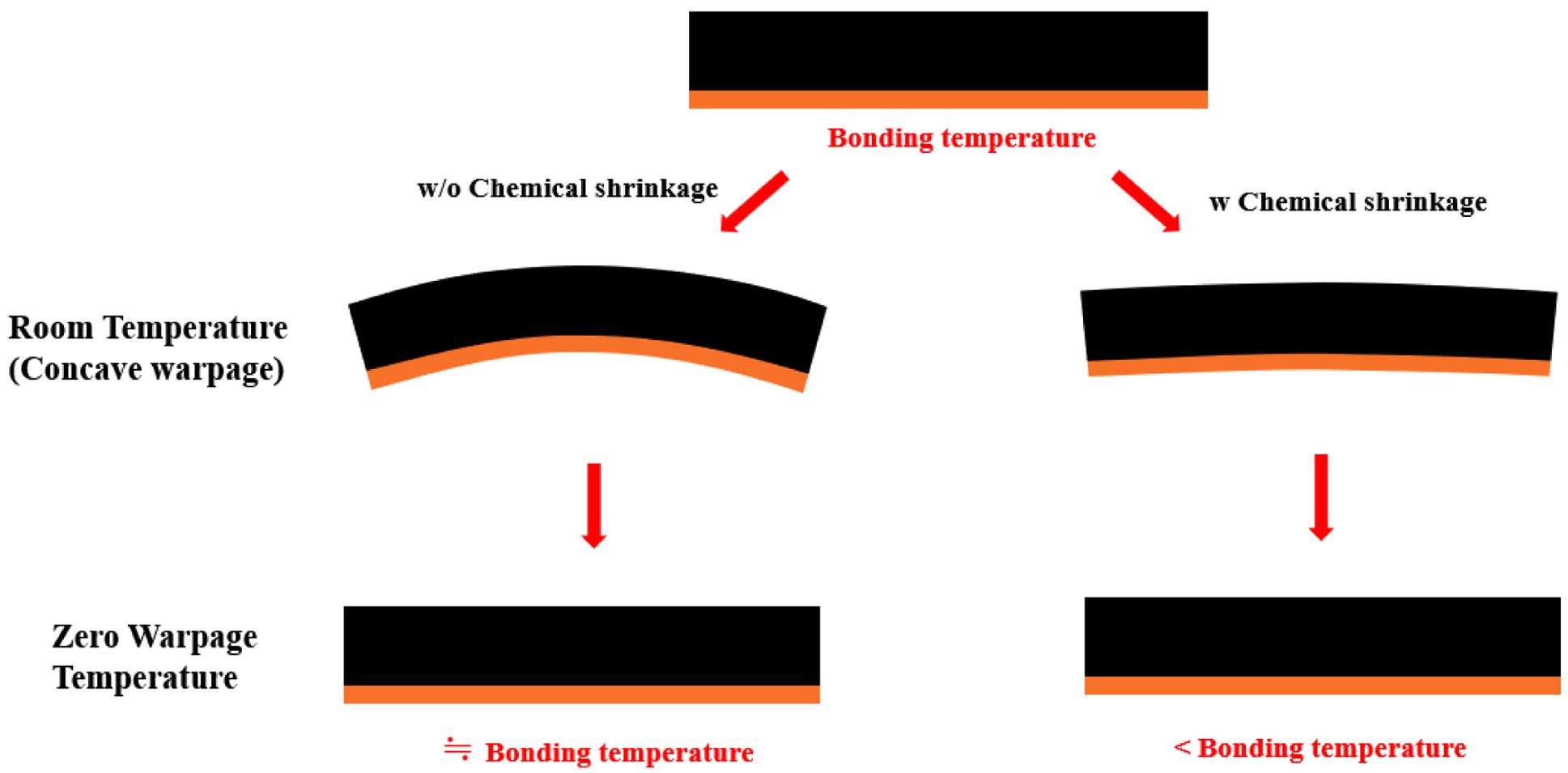

또한, Fig. 7에서 볼 수 있듯이, EMC 경화 과정 중 발생하는 Chemical shrinkage에 의해서 휨이 상대적으로 감소하여 Bonding 온도보다 낮은 온도에서 Zero 휨 온도가 발생하게 된다[9]. 추후, Chemical shrinkage를 분석하여 Bonding 온도를 분석할 예정이다.

|

Fig. 2 Viscosity of EMC according to temperature |

|

Fig. 3 Cure Cycle; (a) Hot Press, (b) CNT Heater |

|

Fig. 4 OM Image; (a) Hot Press, (b) CNT Heater |

|

Fig. 5 Surface & Interface; (a) Hot Press, (b) CNT Heater |

|

Fig. 6 Warpage of EMC/Cu Bi-layer Package according to temperature; (a) Hot Press, (b) CNT Heater |

|

Fig. 7 Zero warpage analysis |

본 연구에서는 CNT Heater를 도입하여 EMC/Cu Bi-layer 패키지의 새로운 공정 방법을 제시하였다. 기존의 Hot Press 공정과 CNT Heater 공정을 통해 EMC/Cu Bi-layer 패키지를 제작하였으며, 아래와 같은 결과를 얻었다.

1) Hot Press와 CNT Heater를 이용해 제작한 EMC 내부의 Void가 없는 것을 확인하였다.

2) Hot Press와 CNT Heater를 이용하여 제작한 EMC/Cu Bi-layer의 계면에 Void가 없는 것을 확인하였으며, 접합이 잘 이루어진 것을 확인하였다.

3) EMC/Cu Bi-layer Package의 휨 분석 결과, 상온에서의 Convex 휨, Zero 휨 온도, 휨 크기가 증가에서 감소로 바뀌는 온도가 두 공정 모두 동일한 것을 통해 CNT Heater를 통한 전자 패키징 공정의 가능성을 확인하였다.

본 연구는 2020년도 산업체연구개발사업의 재원으로 한국의 삼성전자의 지원을 받아 수행한 연구 성과입니다. (G01190544).

- 1. Lu, D., and Wong, C.P. (Eds.), “Materials for Advanced Packaging”, Vol. 181, New York: Springer, 2009.

-

- 2. Li, Y., and Goyal, D. (Eds.), “3D Microelectronic Packaging: from Fundamentals to Applications”, Vol. 57, Springer, 2017.

-

- 3. Centea, T., and Nutt, S.R., “Manufacturing Cost Relationships for Vacuum Bag-only Prepreg Processing”, Journal of Composite Materials, Vol. 50, No. 17, 2016, pp. 2305-2321.

-

- 4. Witik, R.A., Gaille, F., Teuscher, R., Ringwald, H., Michaud, V., and Månson, J.-A.E., “Economic and Environmental Assessment of Alternative Production Methods for Composite Aircraft Components”, Journal of Cleaner Production, Vol. 29, 2012, pp. 91-102.

-

- 5. Monaghan, P.F., and Brogan, M.T., “An Overview of Heat Transfer for Processing Thermoplastic Composites in Autoclaves”, Proc Flow Processes in Composites Materials Conference. 1991.

- 6. Chien, A.T., Cho, S., Joshi, Y., and Kumar, S., “Electrical Conductivity and Joule heating of Polyacrylonitrile/Carbon Nanotube Composite Fibers”, Polymer, Vol. 55, No. 26, 2014, pp. 6896-6905.

-

- 7. Mohiuddin, M., and Hoa, S.V., “Temperature Dependent Electrical Conductivity of CNT–PEEK Composites”, Composites Science and Technology, Vol. 72, No. 1, 2011, pp. 21-27.

-

- 8. Lee, J., Ni, X., Daso, F., Xiao, X., King, D., Gómez, J.S., Varela, T.B., Kessler, S.S., and Wardle, B.L., “Advanced Carbon Fiber Composite Out-of-autoclave Laminate Manufacture via Nanostructured Out-of-oven Conductive Curing”, Composites Science and Technology, Vol. 166, 2018, pp. 150-159.

-

- 9. Tsai, M.Y., Ting, C.W., Huang, C.Y., and Lai, Y.S., “Determination of Residual Strains of the EMC in PBGA during Manufacturing and IR Solder Reflow Processes”, Microelectronics Reliability, Vol. 51, No. 3, 2011, pp. 642-648.

-

This Article

This Article

-

2021; 34(1): 47-50

Published on Feb 28, 2021

- 10.7234/composres.2021.34.1.047

- Received on Dec 29, 2020

- Revised on Feb 16, 2021

- Accepted on Feb 24, 2021

Services

Services

Shared

Correspondence to

Correspondence to

- Seong Su Kim

-

Department of Mechanical Engineering, KAIST

- E-mail: seongsukim@kaist.ac.kr

Copyright ⓒ The Korean Society for Composite Materials. All rights reserved.

Copyright ⓒ The Korean Society for Composite Materials. All rights reserved.